MOS

| Type     | Catalog Number | Package |  |

|----------|----------------|---------|--|

| SDA 2006 | Q67100-Q264    | DIP-18  |  |

#### **General Features**

- Electrically programmable non-volatile memory fabricated in n-channel floating-gate technology

- Memory capacity: 512-bits (32x 16-bit words)

- Serial address, chip-select, and command input by 8 or 12-bit control words (length selectable by external connection).

- Erase and write duration set by external control

- Signal outputs are open-drain; active signal inputs and outputs invertible via external wiring

- Reprogrammable over 10<sup>4</sup> times

- Unlimited read without data loss

- Data retention of at least10 years

## **Absolute Maximum Ratings**

| Supply voltage Supply voltage Supply voltage Input voltage Total power disspiation | $\begin{array}{c c} U_{DD  2\text{-}1} \\ U_{PI  18\text{-}1} \\ U_{PH  3\text{-}1} \\ U_{I\text{-}17} \\ P_{tot} \end{array}$ | 22<br>22<br>41<br>16<br>400 | V<br>V<br>V<br>V<br>mW |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------|

| Thermal resistance (junction to air) Storage temperature                           | $\begin{matrix} R_{th  SU} \\ T_S \end{matrix}$                                                                                | 90<br>-40 to 125            | K/W<br>°C              |

| <b>Typical Operating Ratings</b> $(U_{SS} = 0V)$                                   |                                                                                                                                |                             |                        |

| Supply voltage<br>Operating temperature                                            | $\begin{array}{c c} U_{DD2\text{-}1} \\ T_U \end{array}$                                                                       | 11-16<br>0 to 70            | V<br>°C                |

| Statistical characteristics $(U_{SS} = 0 \text{ V})$                                                                                    |                                                                                                 |     |                     |                               |                     |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|---------------------|-------------------------------|---------------------|

| _                                                                                                                                       |                                                                                                 | min | typ                 | max                           |                     |

| Supply current Substrate bias Substrate current                                                                                         | $I_{DD\;2} \\ -U_{BB\;1}$                                                                       | 4   | 10                  | 20<br>6                       | mA<br>V             |

| (medium current) (pulsed max current) Programming voltage Programming current, low current                                              | -I <sub>BB 1 m</sub> *)<br>-I <sub>BB 1 s</sub> *)<br>U <sub>PH 3</sub> *)<br>I <sub>PH 3</sub> |     | 0.5<br>33<br>0.1    | 2<br>10<br>35                 | mA<br>mA<br>V<br>mA |

| Programming current, medium current Programming current, pulsed max current Write voltage Write current, low current                    | I <sub>PH 3 m</sub> I <sub>PH 3 s</sub> U <sub>PH 18</sub> *) I <sub>PI 18</sub>                |     | 2<br>5<br>15<br>0.1 | 5<br>10<br>16                 | mA<br>mA<br>V<br>mA |

| Write current, medium current Write current, pulsed max current                                                                         | $I_{PI~18~m}$ $I_{PI~1s~s}$                                                                     |     | 5<br>15             | 20 20                         | mA<br>mA            |

| Inputs                                                                                                                                  |                                                                                                 |     |                     |                               |                     |

| $D_i$                                                                                                                                   | $U_{L8,12,16}$                                                                                  | 0   |                     | 0.5                           | V                   |

| $\Phi  /  \overline{\Phi}$                                                                                                              | $U_{H8,12,16}$                                                                                  | 4   |                     | $ m V_{DD}$                   | V                   |

| $\begin{aligned} & \text{REC/}\overline{\text{REC}} \\ & & (\text{U}_{\text{H}} = \text{U}_{\text{DD}}) \\ & \text{STWL} \end{aligned}$ | I <sub>H 8,12,16</sub>                                                                          |     |                     | 10                            | μА                  |

| $(-I_L = 100 \mu A, Pull-up-Resistors)$<br>INV<br>$CS_3$<br>$CS_1, CS_2$                                                                | $\begin{array}{c} U_{L4,15,9,11,10} \\ U_{H4,15,9,11,10} \\ I_{H4,15,9,11,10} \end{array}$      | 0 4 |                     | 0.5<br>V <sub>DD</sub><br>10  | V<br>V<br>μA        |

| (Only with 12-bit word, $U_H=U_{DD}$ )<br>$\frac{(U_L = 0V; U_H = V_{DD})}{\overline{RES}}$                                             | $I_{H\ 4,15,9,11,10} \\ I_{L\ 4,15,9,11,10} \\ U_{L\ 6}$                                        | 0   |                     | 10<br>300<br>0.5              | μΑ<br>μΑ<br>V       |

| $(U_{L} = 0V)$ $(U_{H} = V_{DD})$                                                                                                       | U <sub>H 6</sub><br>-I <sub>L</sub><br>I <sub>H</sub>                                           | 4   |                     | V <sub>DD</sub><br>200<br>200 | V<br>μΑ<br>μΑ       |

| Outputs                                                                                                                                 |                                                                                                 |     |                     |                               |                     |

| $D_q/\overline{\overline{D}_q},\overline{\overline{L}}/\overline{L}$                                                                    | $U_{\rm L14,13}$                                                                                |     |                     | 0.5                           | V                   |

| $(I_L = 1 \text{ mA}; \text{ Open Drain Output})$<br>$(U_H = V_{DD})$                                                                   | $I_{L14,13}$                                                                                    |     |                     | 10                            | μΑ                  |

<sup>\*)</sup> required during programming only

| <b>Dynamic</b> | chara   | cteristics   |

|----------------|---------|--------------|

| Dynamic        | Ciiai a | icici istics |

| Bus Φ – Clock INV low Φ – Clock INV high                                 |

|--------------------------------------------------------------------------|

| Settling Time<br>INV high or low                                         |

| Programming Time $(U_{PH} = 33V, U_{PI} = 15V)$<br>Programming Frequency |

|                                                              | min                          | typ | max |                                  |

|--------------------------------------------------------------|------------------------------|-----|-----|----------------------------------|

| $egin{array}{l} t_{H} & & & & & & & & & & & & & & & & & & &$ | 5<br>10<br>10<br>5<br>5<br>5 |     | 2   | μs<br>μs<br>μs<br>μs<br>μs<br>μs |

| $t_{prog}$                                                   |                              | 0.1 | 1   | S                                |

| $f_{prog}$                                                   |                              |     | 1   | Hz                               |

**INV Low**

**Settling Time**

### **Functional Description**

#### **Data Transfer**

The SDA 2006 uses a 5-line serial bus for communicating data and commands. This bus consists of the following lines:

Data Input D<sub>i</sub>

Data Output  $D_q/\overline{D_q}$

Receiving Data REC/REC (receive data)

Clock Input  $\Phi/\overline{\Phi}$

Programming signal  $\overline{L}/L$  (load)

The active state (low or high) of each of these lines is set with the INV input to facilitate different application circuits.

| Connection                             | State                  |                         | Notes              |

|----------------------------------------|------------------------|-------------------------|--------------------|

| INV                                    | low (U <sub>SS</sub> ) | high (U <sub>DD</sub> ) |                    |

| $\mathrm{D_q}/\overline{\mathrm{D_q}}$ | $D_i = D_q$            | $D_i = \overline{D_q}$  |                    |

| REC/REC                                | high                   | low                     | During data input  |

| $\Phi  /  \overline{\Phi}$             | high                   | low                     | Active clock phase |

| $\overline{\mathrm{L}}/\mathrm{L}$     | low                    | high                    | While programming  |

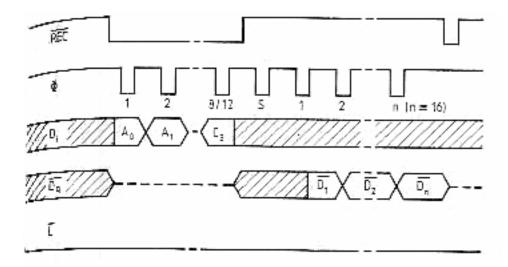

## **Chip Commands**

Commands are sent to the chip via the data input,  $D_i$ . Commands are in the form of a control word whose length is set by the STWL input.

| STWL connection     | low   | $high \ (V_{DD} \ or \ high \ impedance)$ |

|---------------------|-------|-------------------------------------------|

| Control word length | 8-Bit | 12-Bit                                    |

The control words encode the address of the data word to be read or modified, the chip address, and the command. They have the following format. (A0, the LSB, is sent first)

| 8-Bit Control Word  | $A_0A_1A_2A_3A_4B_1B_2C_3$             |

|---------------------|----------------------------------------|

| 12-Bit Control Word | $A_0A_1A_2A_3B_0B_1B_2B_3A_4C_1C_2C_3$ |

$\begin{array}{cccc} \text{where} & A_0 & \dots & A_4 & \text{are address bits} \\ & B_0 & \dots & B_3 & \text{are command bits} \\ & C_1 & \dots & C_3 & \text{are chip select bits} \end{array}$

| Comman | d | Codes: |

|--------|---|--------|

| Comman | u | Coucs. |

|                | 12-bit Co          | ommand Word    | _     |                                 |

|----------------|--------------------|----------------|-------|---------------------------------|

| $\mathrm{B}_0$ | $B_1$              | $\mathrm{B}_2$ | $B_3$ | Command                         |

| low            | high               | high           | high  | Read out, D <sub>9</sub> as LSB |

| low            | low                | high           | high  | Read out, D <sub>1</sub> as LSB |

| low            | low                | low            | high  | Program                         |

|                | 8-bit Command Word |                |       |                                 |

#### **Chip select:**

Memory contents are decoded only when the chip select bits agrees with the chip select inputs and a read out command has been sent.

| Chip Selec         | t - Pin         | Chij                                            | Select - Bit   |                     |

|--------------------|-----------------|-------------------------------------------------|----------------|---------------------|

|                    | -               | $\leftarrow \rightarrow \leftarrow \rightarrow$ | -              | 12-Bit Control Word |

| 8-Bit Control Word | CS <sub>3</sub> | $\leftarrow \rightarrow$                        | C <sub>3</sub> | ]                   |

CS<sub>1</sub> and CS<sub>2</sub> are inactive with 8-bit control word.

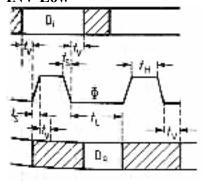

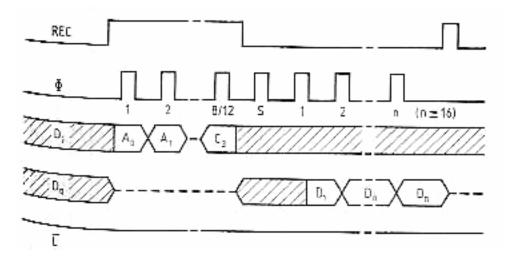

### **Reading** (Fig. 1a and b)

Before reading, the 8- or 12-bit control word must be clocked in at the data-input  $D_i$ . 8 (or 12) clock pulses are required on the  $\Phi/\overline{\Phi}$  pin to enter the control word. While entering the control word the REC/ $\overline{REC}$  pin needs to be held in the active state. (Note that REC is active high when the INV pin is low and active low when the INV pin is high).

At the falling edge of the REC/REC pin, the command word is decoded and compared to the chip select pins. If they agree the data output  $D_q/\overline{D_q}$  becomes low-impedance.

The read-out process is started with an additional clock pulse S. A new bit of data is output on each subsequent falling edge of the clock. The LSB is available on the data output on the first of these pulses. The control word can identify either the first bit D1 or D9 as the LSB during the read-out. The read-out process can be canceled after any number of shift impulses. Every saved 16-bit word is divided into two 8-bit words and can be read out as thus.

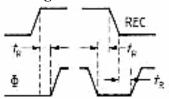

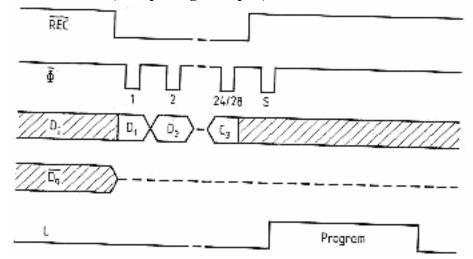

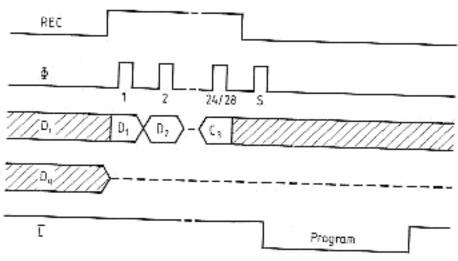

#### **Programming** (Fig. 2a and b)

Before programming, the 16-bit data word (D1 as LSB) and the 8/12-bit control word must be clocked in on data input  $D_i$  with REC/ $\overline{REC}$  active. Upon the rear edge of the REC/REC signal, the programming command is decoded. However, the re-programming process begins only after the rear edge of an additional clock pulse. When the programming process begins the  $\overline{L}/L$  signal is activated.

The programming duration  $T_{Prog}$  is set by internal control. Regardless of the external control voltages  $U_{PH}$  and  $U_{PI}$ , the erase and write processes do not end until the entire memory has reached the desired state. While programming no external signals should be applied to the chip because the inputs REC/ $\overline{REC}$ ,  $\Phi/\overline{\Phi}$ , and  $D_i$  are inactive. The process can only be prematurely interrupted with a low on the  $\overline{RES}$  pin.

#### **Reset function**

A low voltage on input  $\overline{RES}$  brings the memory to its reset state. The input has an internal voltage divider which ensures the chip is not in its reset state when  $V_{DD} > 11 \text{ V}$ .

### **Voltages**

The SDA 2006 has four power pins,  $U_{PH}$ ,  $U_{PH}$ ,  $U_{DD}$ , and  $U_{BB}$ , which are all referenced to  $U_{SS}$  (ground connection). In most applications  $U_{DD}$  and  $U_{PI}$  are connected together.  $U_{PH}$  and  $U_{PI}$  are only required during programming. They can be open or at ground during read-out and when the chip is inactive. The levels of these voltages affect only the duration, not the reliability of the non-volatile storage process.

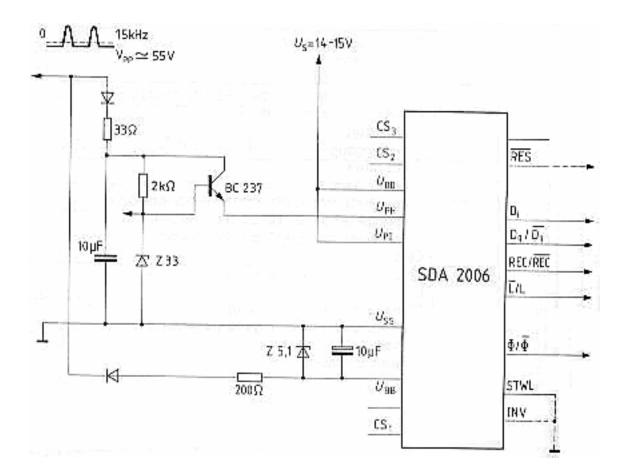

Fig. 3 shows a practical circuit of a TV tuning-memory.

## Inverted levels (INV pin high or open)

Fig. 1a

# Non-Inverted levels (INV pin low)

Fig. 1b

Figs. 1a and 1b show the read process (only active levels provided/specified)

# Inverted levels (INV pin high or open)

Fig. 2a

Figs. 2a and 2b show the programming process (only active levels provided/specified)

# **Pin Configuration**

| Pin Number | Symbol                                 | Function                                       |

|------------|----------------------------------------|------------------------------------------------|

| 1          | $U_{BB}$                               | Substrate bias                                 |

| 2          | $\mathrm{U}_{\mathrm{DD}}$             | Supply voltage                                 |

| 3          | $\mathrm{U}_{\mathtt{PH}}$             | Programming voltage                            |

| 4          | STWL                                   | Length of control word 12 / 8 bit (input),     |

|            |                                        | (12-bit for high or no connection)             |

| 5          |                                        | No Connection                                  |

| 6          | RES                                    | Reset input                                    |

| 7          |                                        | No Connection                                  |

| 8          | $D_{i}$                                | Data input                                     |

| 9          | $CS_3$                                 | Chip select inputs (8 and 12-bit control word) |

| 10         | $CS_2$                                 | Chip select input (12-bit control word)        |

| 11         | $CS_1$                                 | Chip select input (12-bit control word)        |

| 12         | $\Phi / \overline{\Phi}$               | Clock input *)                                 |

| 13         | L/L                                    | Programming signal output (load) *)            |

| 14         | $\mathrm{D_q}/\overline{\mathrm{D_q}}$ | Data output *)                                 |

| 15         | INV                                    | Invert input signals (input)                   |

| 16         | REC/REC                                | Data-input control (receive) *)                |

| 17         | $U_{SS}$                               | Ground                                         |

| 18         | $U_{PI}$                               | Write Voltage                                  |

<sup>\*)</sup> First polarity for INV low. Second polarity for INV high.

Fig 3: SDA 2006 as TV tuner-memory